新闻动态

NEWS

高速背板设计案例

发布时间:2023-06-29 17:24

类别 | 高速背板 |

产品所属行业 | 网络产品 |

单板类型 | 背板 |

Pin数 | 18173 |

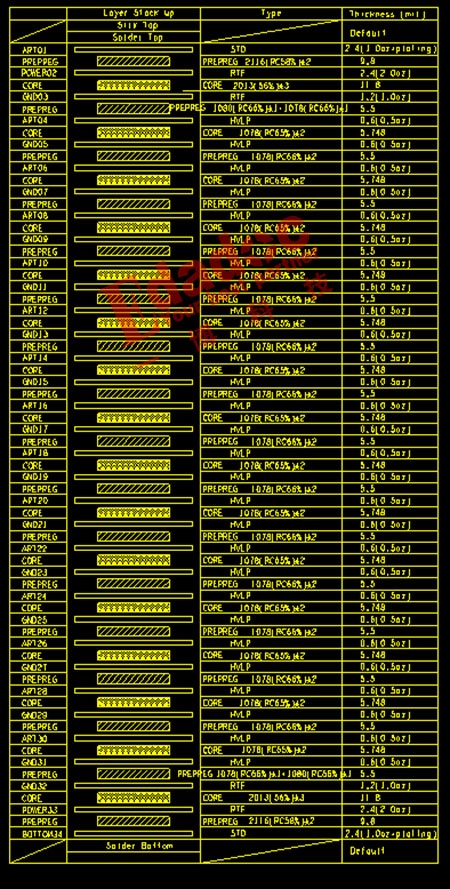

层数 | 34 |

最高信号速率 | 56G |

难点 | 1、 信号线速率高,对于板材选用有很大局限;单板高速线多,对层数和成本又有控制; 2、 单板上有48V高压电源,电流大; 3、 结构限制,布线和电流瓶颈多;单板高速线之间的互穿,串扰严重; 4、 背钻设计; |

我司对策 | 1、 由于单板大部分都是56G的高速线,部分的25G、10G的信号,经过我司SI仿真,为保证信号质量,我们推荐用M7NE板材,减小损耗; 2、 单板高速线经评估后需要14个布线内层;电源电流较大,规划了2个电源层(2OZ),总设计34层,板厚6MM,具体层叠如下:

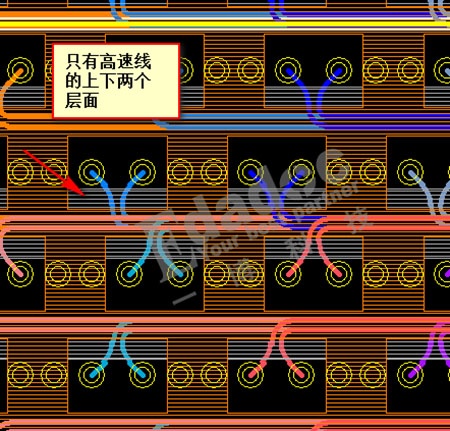

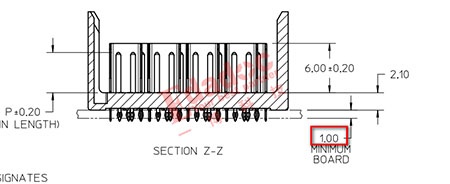

3、 48V高压电源保证期相邻层有自身的回流高压GND,如电源走在第2层,它的回流GND放在top层;由于电源较大,其它层有加强,对应相邻的层铺上回流GND;同时与板内大地保持足够的安全间距(挖空几层); 4、 单板信号速率高,考虑TX穿RX连接器铜柱的串扰,把连接器(如连接器在BOT层)里面的线走在上面的层,外面的走在下面的层,这样背钻的时候是从上向下钻,就会把外面的铜柱钻了,避免走线穿铜柱带来的串扰; 5、 高速线PIN角处有做焊盘优化;

6、 因为高速连接器正反两面都有,考虑连接器PIN的STUB长度和背钻,设计层叠时把电源层放在第2层和第33层,高速线走在单板的中间,这样背钻后的stub最短;

|