DDRx仿真

仿真难点

- 走线密度大,颗粒数量多,运行速率高、时序裕量小,驱动种类多

仿真目的

- 指导Layout布局布线

- 项目调试中出现问题,通过仿真定位问题并提出改进意见

- 测不到芯片内部的信号,通过仿真对比外部测试数据,模拟到芯片内部的真实情况

仿真内容

- 拓扑优化,ODT调节,驱动选择,端接/串阻阻值调节,时序分析,针对所有信号线进行全通道仿真

仿真意义

- 指导Layout布局布线

- (LP)DDR3/4/5、GDDR6拓扑类型选择

- 低功耗要求时,能否关掉ODT也能正常工作

- (LP)DDR3/4/5、GDDR6在高密度、降成本(如减层、用普通工艺)时的设计指导

- HDI设计时无完整参考平面或者无法很好等长时布线指导

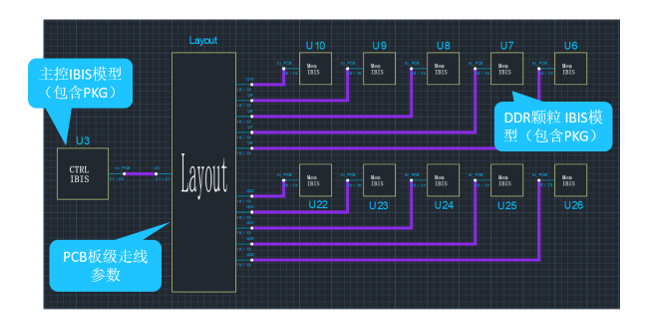

仿真对象

DDR(LPDDR)3/4/5全通道仿真

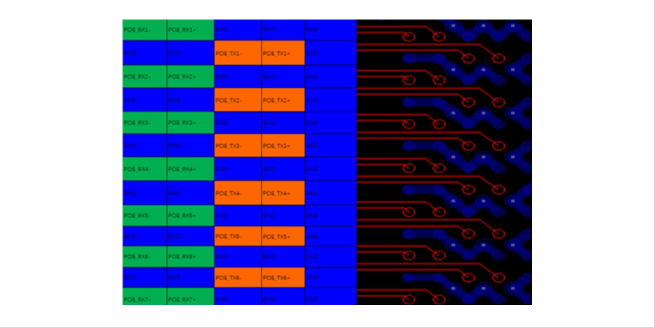

某国产CPU芯片 DDR5-1拖10拓扑板载颗粒全通道仿真案例

某国产CPU-DDR5全通道仿真案例

设计经验

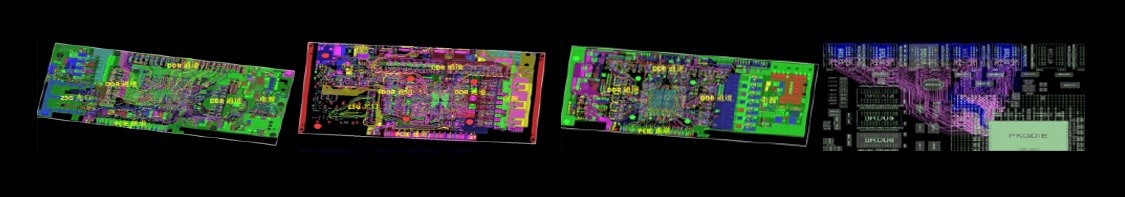

一博科技每年15000款以上的设计经验,铸就了业内领先的DDR仿真技术

下图为近年来热门的AI人工智能的加速卡设计,高难度的设计和仿真帮助内外AI公司快速推出其产品

密集多通道LPDDR5算力卡,运行速率6400Mbps

仿真内容

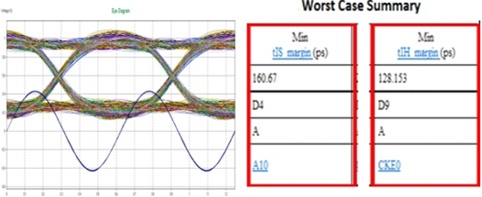

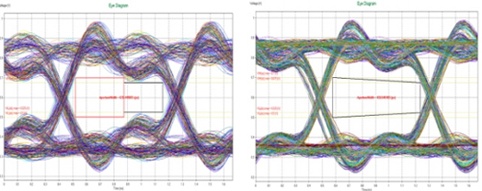

信号质量仿真:

-仿真优化前后结果对比

信号时序仿真:

-各组信号时序关系对应

-时序窗口计算(建立/保持时间Margin)