你想要的过孔和加工出来的过孔有多大差别?

发布时间:2023-09-19 15:55

作者:一博科技高速先生自媒体成员 黄刚

在高速PCB设计中,过孔的影响力不言而喻,一个优化不好的过孔就可以把整个链路的性能降低一个level!更重要的是如果你觉得你在PCB设计上优化好了,加工出来就一定是这个样子的话,那你就…

高速先生文章其实关于过孔的影响已经写过很多篇文章了,包括了它的各部分结构是如何影响阻抗的;它的过孔stub是如何对信号造成致命影响的;它在不同层的出线也会有着不同的阻抗表现等等的文章,大家都可以往前去再翻阅一下哈。

但是今天我们要说的是设计与加工的误差,再细致的说,今天讲的是过孔的设计孔径和实际加工出来的孔径的差异,因为根据我们之前说过的文章,孔径对于过孔阻抗的影响也是很大的,而且过孔孔径越大,过孔的阻抗就越低。本来都已经很难把过孔的阻抗做到单端50或者差分100欧姆了,再加上加工之后就更难了。因此我们今天通过自己做的一块测试板的仿真和测试让大家知道设计孔径和加工出来的孔径其实是存在差异的哈!

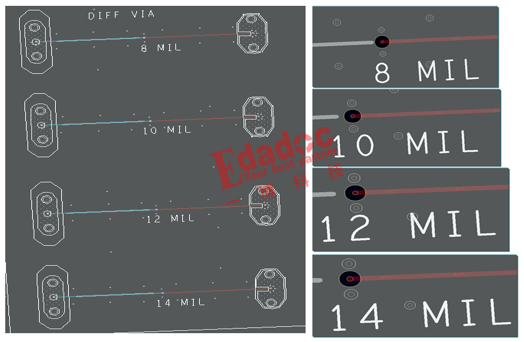

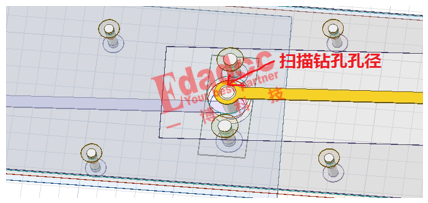

我们的测试板分别设计了8mil,10mil,12mil和14mil的四种孔径的过孔,如下所示:为了保证变量的单一性,我们把过孔的反焊盘大小和与旁边地过孔的位置距离都做成一样,唯一的变量就是过孔的孔径(以及过孔对于的pad)。

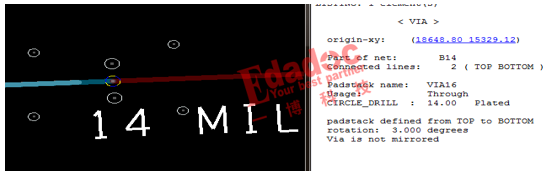

那我们要怎么才能知道设计与加工的误差呢?方法也很简单,下面我们拿14mil的过孔举例说明我们的验证方法。

我们首先知道PCB设计上的14mil过孔实际上指的是加工电镀完后的孔径为14mil,,如下所示:

大家肯定也知道,如果要在加工后达到14mil的完成孔径,那钻孔孔径肯定是需要大于14mil的,因为在钻孔完成后需要对孔壁进行电镀,保证垂直方向的连通性。

那么钻孔的大小就是我们所关心的参数了,它直接和我们的阻抗所挂钩。因为我们就可以去模拟钻孔的大小对该过孔模型进行扫描仿真了。

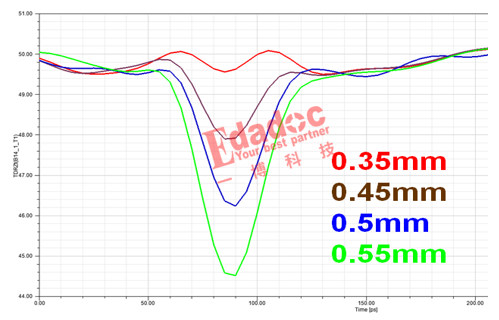

那我们就能通过仿真得到不同钻孔孔径时这个过孔的阻抗情况了,如下所示:从0.35mm的14mil到0.55mm的22mil钻孔孔径时的过孔阻抗。从仿真结果能看到,变化2mil钻孔孔径时对过孔的阻抗来说也是不小的变化。原本14mil设计过孔阻抗刚好能达到50欧姆,随着加工的孔径越来越大之后,真实的阻抗也是慢慢的往下降了。

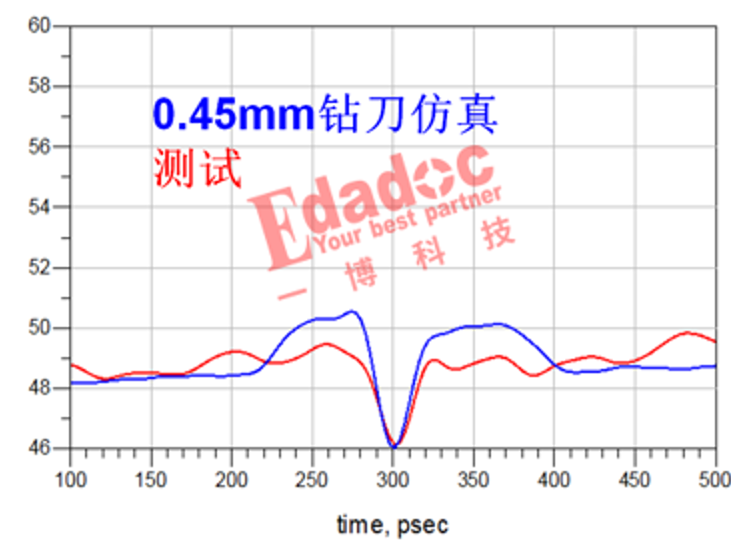

那么你们所好奇的这个14mil的设计孔径,板厂默认会用多大钻刀去钻孔呢?高速先生既然已经把这块测试板做出来了,肯定是它的测试数据,我们逐一把仿真结果和测试结果进行对比,发现0.45mm钻孔孔径的仿真结果和真实的测试结果能更好的拟合上。也就是说,对于这个设计孔径14mil的过孔来说,工厂会用0.45mm也就是18mil的钻刀进行钻孔,然后再电镀成14mil的完成孔径!

当然其他孔径的过孔,高速先生也做了类似的仿真测试验证,来证明板厂对不同设计孔径所使用的钻刀大小,这里由于篇幅关系就不一一列举了。高速先生通过这篇文章想告诉大家的是,我们在进行过孔的PCB设计时,一定要提前估计到它在加工后的一些变化,尤其是在高速设计中,它的加工变化对通道的性能会产生不小的影响,要把这部分的裕量预留出来才是一个优秀的PCB设计!