深度揭秘,阻抗测试那些你所不知道的内幕

发布时间:2021-07-05 11:44

作者:一博科技高速先生自媒体成员 周伟

最近,新晋级的SI攻城狮雷豹运气有点霉,刚刚经受了Pin delay的折磨,现在又碰到一个怪异的事情,某客户产品性能有问题,经多次排查后,发现板内阻抗测试结果不达标,但是板厂的出货报告,却显示阻抗值达标。这让雷豹犯了难,到底该相信谁呢?唉!真是屋漏偏逢连夜雨,船迟又遇打头风,刚转SI不久,偏偏问题却都集中爆发,难道问题会欺生?

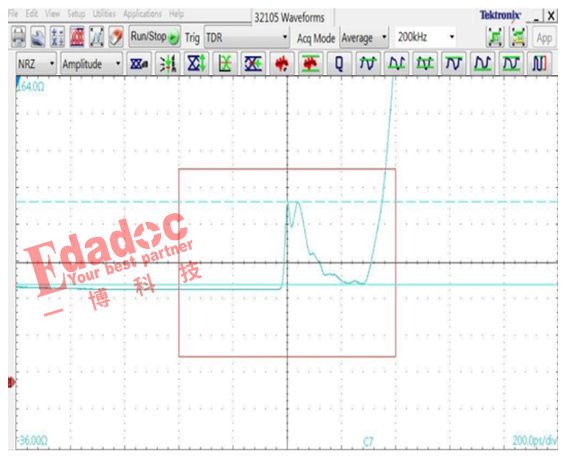

还好雷豹没有自暴自弃,也没有被问题吓倒,因为他的身后还有他的师傅,为他遮风挡雨,排忧解难。于是他把客户发给他的阻抗测试图片给师傅看了一眼,阻抗结果是这样的:

师傅定睛一看,然后就轻轻的转过头瞟了他一眼,反问道:“你确定这个客户会测试阻抗吗?”

这问题问得雷豹丈二和尚摸不着头脑,作为新人还没有开始接触阻抗测试方面的培训,更没有摸过阻抗测试仪(TDR),只是以前在做PCB设计时,和工厂的EQ工程师沟通阻抗时,听那人说过阻抗测试就是:

袖子一挽

探头一点

数据显现

截图交单

但真的是这样吗,雷豹不敢说,怕说错了引来师傅的暴雷。

于是他摇了摇头。

还好他平日勤奋好学,态度又端正,深得师傅喜欢,不待雷豹开口,师傅就抢先说道:“任何测试都是有判断标准的,阻抗测试也是,并不是随便测个图形就能说明有无问题,还要看这个测试本身的图形是否规范,如果没有按照要求来进行的测试,测出来的结果可能就没有任何意义,有时甚至带来负面影响,导致问题的定位朝着错误的方向发展,最终钻进了死胡同,找不到问题不说,反而会耽误很多时间,这个是我们debug的大忌。”

师傅看雷豹听得入神,端起茶杯,慢慢地呷了一口水,继续说道:

“阻抗测试的标准或者说规范,其实也没有一个公认的标准组织来制定,目前坊间流传最广的一个是IPC的测试标准,另一个是Intel的测试方法。

IPC的标准简而言之就是待测线路的阻抗线需要完整显示在仪器屏幕上,时间上就是从探头接触点开始到最终开路的位置都需要完整的显示在TDR屏幕上,而测量区间是从整个时间段的30%~70%时间区域,也就是说示波器的读数是在这个区域内进行的最大最小取值,如下图所示。

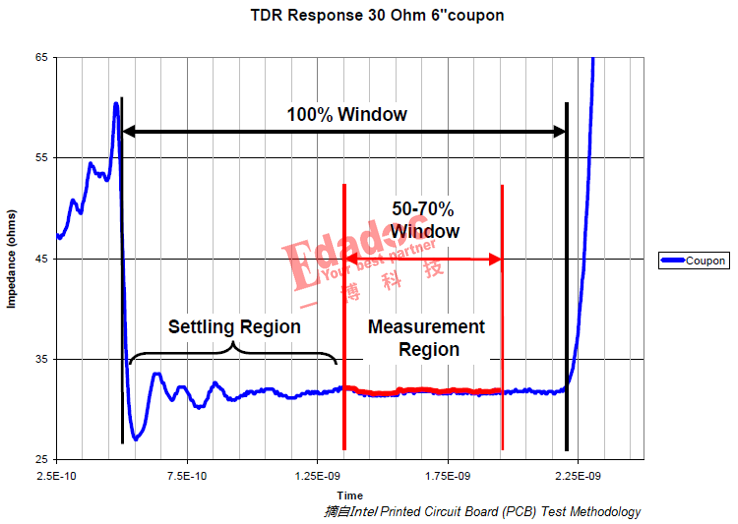

而Intel采用了一种更平均的方法,要求似乎放得更宽,它的测量区间为整个线路时间段的50%~70%区域,如下图所示。

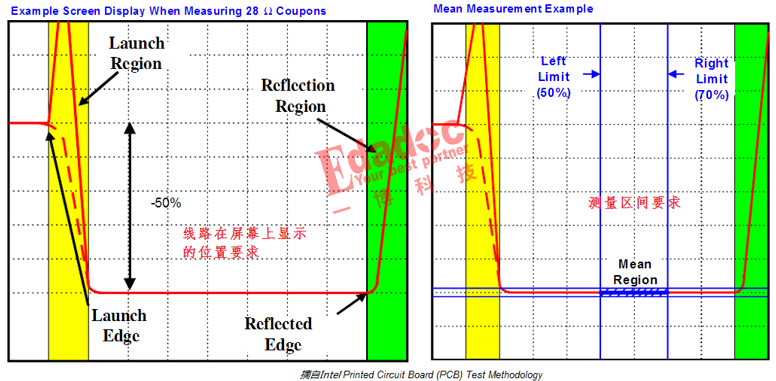

结合泰克的TDR仪器,对测试进行了进一步的规范,同时对起始点和末端开路点显示也做了一定的要求,测量平稳状态基本在20%~90%段的屏幕区间上,而取值是按照50%~70%的屏幕区间进行,具体如下图所示。

Intel的这个方法被大多数PCB板厂所接受,所以现在国内的主流板厂在出厂报告上所测试的阻抗值都是基于50%~70%这个范围区间,只要这个范围阻抗不超标,那么板厂的制板就是满足要求的,并且因为板内阻抗线数量众多,很难一一实测,所以PCB工厂测试的线路也并非板内实际走线,而是板边附带的阻抗Coupon条,这和板内的实际情况多少还是有点差别。”

雷豹被师傅高深莫测的学识深深震撼,完全沉浸在对师傅如滔滔洪水般的敬仰中而不可自拔。他痴痴的望着师傅,绝对是一个虔诚的弟子。

师傅看着他的神情,这时又卖了个关子,问道:“你现在可知道我开始问你的答案是什么了?”

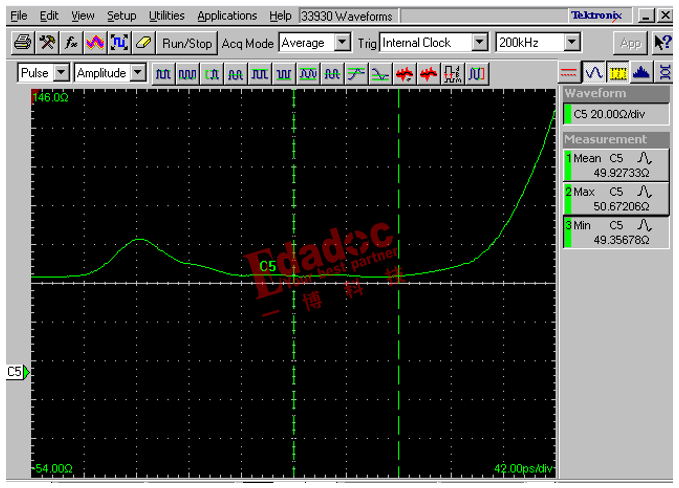

雷豹赶忙从一愣神中惊醒过来,心想还好自己头脑反应快接受能力强,经师傅轻轻一点拨,确实明白了很多,于是就非常自信地回道:“现在看来,这个客户确实不是很懂阻抗测试,从提供的测试图片来看,线路时间没有分布在整个屏幕上,另外也没有测量区间,测量的时间及阻抗刻度都很大,看不出具体的数值,可以说这个测试结果没有任何意义,就像师傅前面说的,这种结果可能会误导查找问题的方向,正确的测试结果应该是如下图这样的。”

师傅听了雷豹的回答,内心一片欢喜,心里暗道孺子可教也,又担心徒弟骄傲自满,于是又喜怒不形于色地问道:“既然板厂的出厂报告是满足要求的,从实际工程来讲,是不是就不用怀疑阻抗的问题了呢?”

师傅这一问,正是雷豹之前有点迷惑的地方,“真是知我者师傅也”,

雷豹心里暗暗惊叹师傅的无所不知,心想以后有什么事还是不要做小动作耍小聪明的好,估计是瞒不过师傅的法眼,可是自已又不能在师傅面前露怯,只好硬着头皮说道:

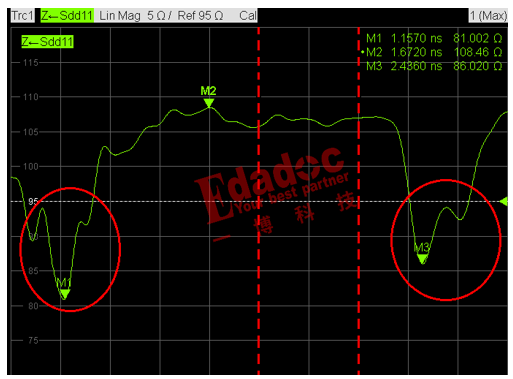

“我猜板厂的阻抗测试只能保证屏幕显示50%~70%那一段线路的阻抗情况,而实际产品是需要看整个线路段的阻抗,很多时候即使板厂的数据是满足要求的,但取值范围外的阻抗有可能超标,而这部分超标的数据是不会显示在阻抗出厂报告里面的,所以我想就算板厂的测试数据是ok的,也不能保证实际线路阻抗就一定没有问题,比如很多时候连接器或者BGA出线处会有过孔,而这个过孔一般是在线路的两端,这个时候过孔的阻抗就不会进入那个阻抗的测试区间,即使阻抗偏低超出要求,板厂的测试数据也不会显示出来,就像下面这个带了芯片的实际产品阻抗测试的图片一样。如下图:

虽然测量区间的结果是满足要求的,但图中M1和M3那两个标示出来的部分应该是过孔或者芯片封装,由于阻抗没有优化到位,这两个部分的阻抗就偏低很多,造成最终整体线路的阻抗不匹配,从而导致信号有比较大的反射,最终影响信号的质量以及系统的工作不稳定如丢包等现象。不知道我的想法对不对,还望师傅指点迷津。”

这就是雷豹令师傅比较满意的地方,果然是天资比较聪颖一点就通,天生就是学习的料,也不妨师傅当初执意要求领导,从几百名设计工程师里面破格挑选出来的一片苦心。问题回答基本上到位了,但还有一点比较关键,师傅觉得有必要再补充一下,于是师傅微微一笑,满意地说道:

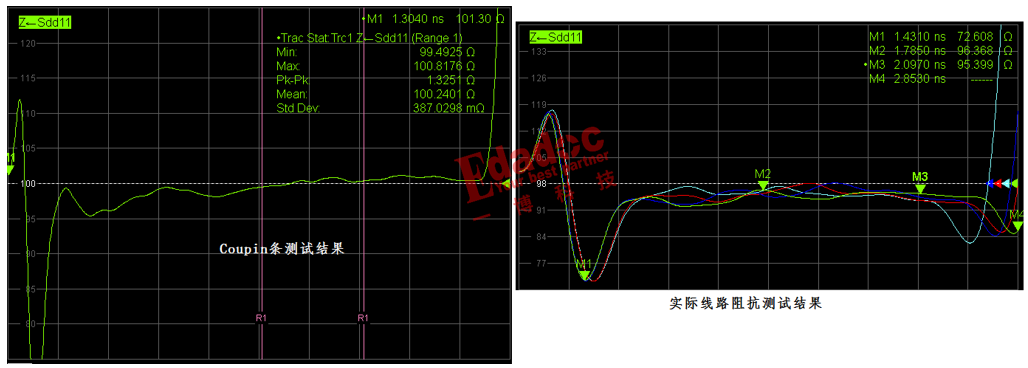

“掌握得差不多了,但还是有点过于理想,我前面其实提到过,板厂的出厂报告测的基本是板边的Coupon条,压根就不会对板内的线路阻抗进行测试,除非客户有图片提出明确的需要在板上哪个位置哪个点进行测试(很少有客户会有这种要求,还要看板厂是否愿意配合),否则板厂是没法找到对应板上的线路进行实测的,因为我们一般提供给板厂的是Gerber光绘文件,板子做出来后,通过这个光绘文件是没法找到具体线路的,所以板厂只能在板边模拟一个和板内实际线宽一致的标准阻抗条来进行测试,这样这个阻抗条线路其实是比较理想的,中间也没有过孔等其他因素的影响,测试出来结果当然就比较理想,这也是为什么很多时候板厂的出厂报告是满足要求的,但实际板上线路阻抗却有较大偏差的原因,可以看看下面图片中阻抗条与板内阻抗的测试结果差异就知道了。”

雷豹暗自感叹:“真是听了师傅一席话,胜读十年书。”但心中不免还是有些疑惑却又不好意思向师傅发问,他的问题是:

为什么阻抗测试范围不能是整个线路段而是30%(50%)~70%段呢?