ESD器件对高速信号有什么影响吗

发布时间:2023-10-24 10:53

我们看到越来越多的工业相机对外的接口信号如USB3/HDMI等在线路上会并(或串)一个ESD器件(或者TVS管),大家觉得针对这种高速接口的信号,ESD器件对信号会有什么影响吗?另外针对这个器件,有些人喜欢叫ESD器件,有些人又喜欢叫TVS管,是不是有点傻傻分不清楚的感觉呢?

要搞清楚这个问题,我们先来简单了解一下什么是ESD器件和TVS管,它们到底有什么作用。

ESD是Electro-Static Discharge的简称,又叫静电放电,是指具有不同静电电位的物体互相靠近或直接接触引起的电荷转移。生活中的静电是人们非常熟悉的一种自然现象,比如小时候经常用笔在头发或毛衣上摩擦几下,就能吸上小小的纸屑,以前觉得可神奇了。静电放电有时候也会把它叫做静电干(骚)扰,如今静电放电已经成为电子产品和设备的一种危害,造成电子产品和设备的功能紊乱甚至部件损坏。现代半导体器件的规模越来越大,工作电压越来越低,导致了半导体器件对外界电磁干扰敏感程度也大大提高。ESD对于电路引起的干扰、对元器件、CMOS电路及接口电路造成的破坏等问题越来越引起人们的重视。ESD也是20世纪中期以来形成的以研究静电的产生、危害及静电防护等为主的学科,电子设备的ESD也开始作为电磁兼容性测试的一项重要内容写入国家标准和国际标准,因此就产生ESD静电保护这么一个元器件产品,国际上习惯将用于静电防护的器材统称为ESD器件。

TVS的全称是Transient Voltage Suppressors,中文叫瞬变电压抑制二极管或瞬态抑制二极管,又叫钳位型二极管,是一种限压保护器件,作用与压敏电阻很类似。也是利用器件的非线性特性将过电压钳位到一个较低的电压值实现对后级电路的保护。它的外型与普通二极管相同,但却能吸收高达数千瓦的浪涌功率;它的主要特点是在反向应用条件下,当承受一个高能量的大脉冲时,它能以10的负12次方秒量级的速度,将其两极间的高阻抗变为低阻抗,吸收高达数千瓦的浪涌功率,使两极间的电压钳位于一个预定值,有效地保护电子线路中的精密元器件,免受各种浪涌脉冲的损坏。当异常的高压消失过后,电路进入到正常工作状态的时候,又恢复到高阻态。

TVS管的作用笼统来说就是在系统中保护电子系统免受高能瞬态脉冲的影响,如静电放电(ESD)、雷电浪涌和电快速瞬态脉冲(EFT),起到防护效果,其具体作用在于:当电路正常工作时,它处于截止状态(高阻态),不影响线路正常工作, 在规定的反向应用条件下,当承受一个高能量的瞬时过压脉冲时,其工作阻抗能立即降至很低的导通值,允许大电流通过,并将电压钳制到预定水平,从而有效地保护电子线路中的精密元器件免受损坏。

典型的 ESD 保护电路由与受保护组件或电路并联放置的 TVS/ESD 二极管组成。在 ESD 事件期间,TVS/ESD 二极管提供接地的低阻抗路径,从而快速钳位电压,将多余的能量从受保护的组件中转移出去。综合来说ESD指的范围更广,不仅是一种器件类型,更是一种事件、一门学科,而TVS管只是消除ESD影响的其中一种器件。

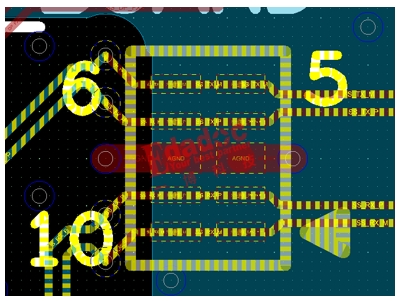

当然,我们今天的话题重点并不是讲ESD器件和TVS管,硬件原理也不是我们擅长的领域,熟悉我们的老铁们应该很清楚,我们主要还是聚焦在和PCB相关上,现在回到我们的正题上,PCB线路上并接了这个ESD器件,有时甚至和走线兼容设计,如下图所示,走线直接穿过ESD器件的焊盘,连接上相当于ESD可有可无,但走线上有了器件,这样对我们的PCB线路会不会有大的影响呢?

气氛都烘托到这个份上了,看来要说没影响估计也没人信了,先来说说我们看到的问题吧。

一个客户在做完产品后测试发现他们的USB3信号眼图很差,如下图所示。

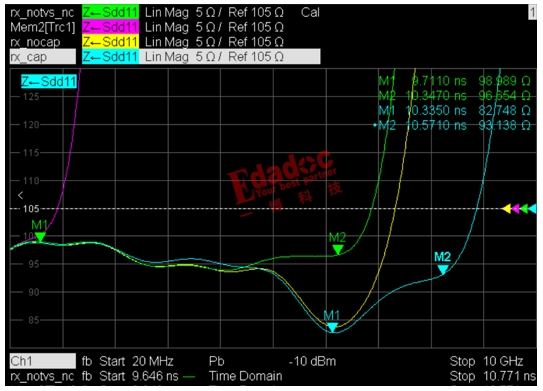

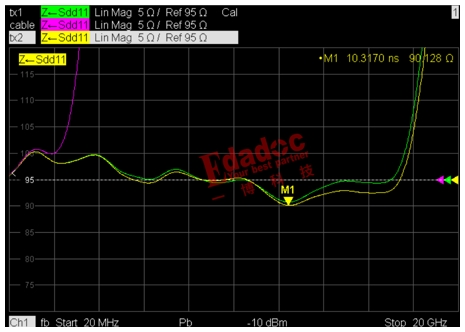

眼图测试显示fail的结果,于是找到我们想帮忙看看到底是哪里出了问题,针对有实际产品的,我们的第一原则就是先测试阻抗摸个底,看看是否阻抗没做好(线路和器件阻抗都有可能没匹配好),于是我们测到了如下图所示的阻抗曲线。

上图最前面那根玫红色的曲线是我们cable断开什么都不接的情况,绿色曲线是去掉ESD器件(TVS管)和后端串联电容的阻抗测试结果,黄色曲线是去掉后端串联电容的阻抗测试结果,湖蓝色(最后面那根)是有ESD器件和电容的阻抗测试结果。可知加上ESD器件后,ESD处线路的阻抗从96ohm跌到了82ohm,阻抗急剧减小,此处对信号来说会有一个比较大的反射,可能是造成眼图变小的一个因素。但前面说过,如果没有这个ESD器件,从功能上来说其实不会有什么影响,但对产品的使用寿命可能会有影响,因为对于外部接口的器件来说,会受到ESD的影响,所以ESD器件的作用就有点像人有时候要买保险,车要买车险是一样的道理,不怕一万,就怕万一,电路也需要保护。在正常的情况下看不到它作用所在,一旦电路出现浪涌、脉冲,静电时,这时候所起的作用就非同小可了,它可保护整个电路体系免受浪涌、脉冲、静电的破坏从而降低损失。所以一般在产品上市之前,国内或国外检测部门都要求进行ESD静电和其它浪涌冲击的测试,确保一切合格才能上市,于是我们就可以看到这个在电路上没有实际功能可有可无的ESD器件忽然变成了不可忽视的存在了。

有时我们在路边摊上买到一个很便宜的电子产品,一开始用起来一切正常,以为自己捡到宝了,但用不了几天发现突然坏了,这个有可能就是因为这些产品没有经过上市前面的各种检测,号称三无产品,也可能没有加ESD器件,在使用过程中被静电打坏了,所以说一分钱一分货哈。

既然一定要这个ESD器件,那么一种ESD器件不行,换另一种是不是就可以了呢?于是客户又找到了另一种ESD器件换上,接下来测试的阻抗结果如下图所示。

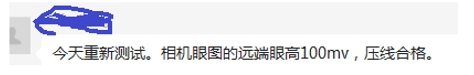

ESD器件最低点的阻抗居然到了90ohm,和USB3的标准阻抗是一样的了,这样阻抗反射的影响就小了很多,接下来再测试下眼图看是不是会好点,虽然后面没有最终的眼图测试结果图片,但客户最终反馈眼图结果合格,至此事情得到完美的解决。

— end —

本期提问

针对高速信号,我们选择ESD器件的时候特别需要在哪些方面要注意呢?